解密英特尔至强6:如何做到处理器性能与能效的平衡?

至强6700E发布:能效核登场,秋季迎来性能核

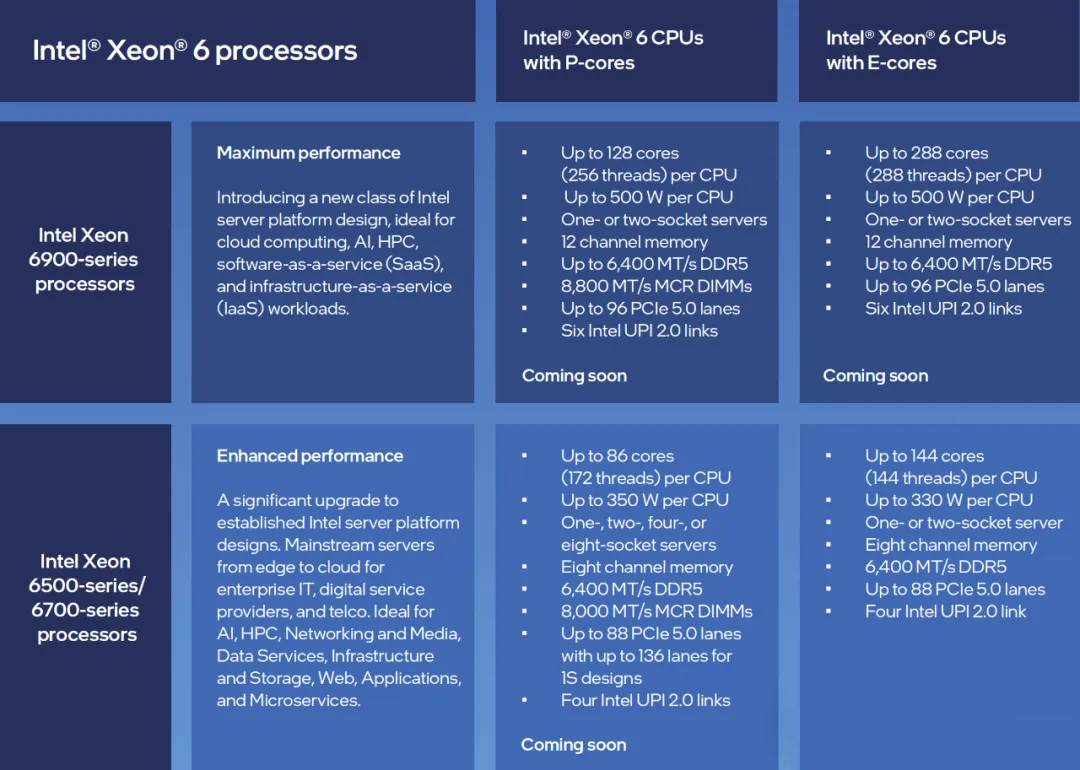

今天,英特尔在Computex 2024首周正式发布了配备能效核(E-cores)的至强6700E处理器。该处理器如期在2024年第二季度推出,为数据中心和企业级应用提供了更高的能效比。与此同时,配备性能核(P-cores)的至强6900P处理器预计将在2024年秋季与大家见面。

根据路线图,2025年第一季度将迎来P和E核的组合新机型――6900E和6700P,此外还有6500P、6300P和至强6 SoC,看起来像是至强D的延续。此前第四、五代采用Chiplet技术的英特尔至强(Xeon)可扩展处理器主要走性能核路线,代号包括Sapphire Rapids(SPR)和Emerald Rapids(EMR)。至强6的性能核版本则延续这一风格,代号为Granite Rapids,而能效核版本将以Forest(森林)结尾,如至强6700E的Sierra Forest。

英特尔继续以创新的架构设计引领处理器市场,进一步推动数据中心的效率和性能提升。

性能核与能效核并驱:创新架构优化计算体验

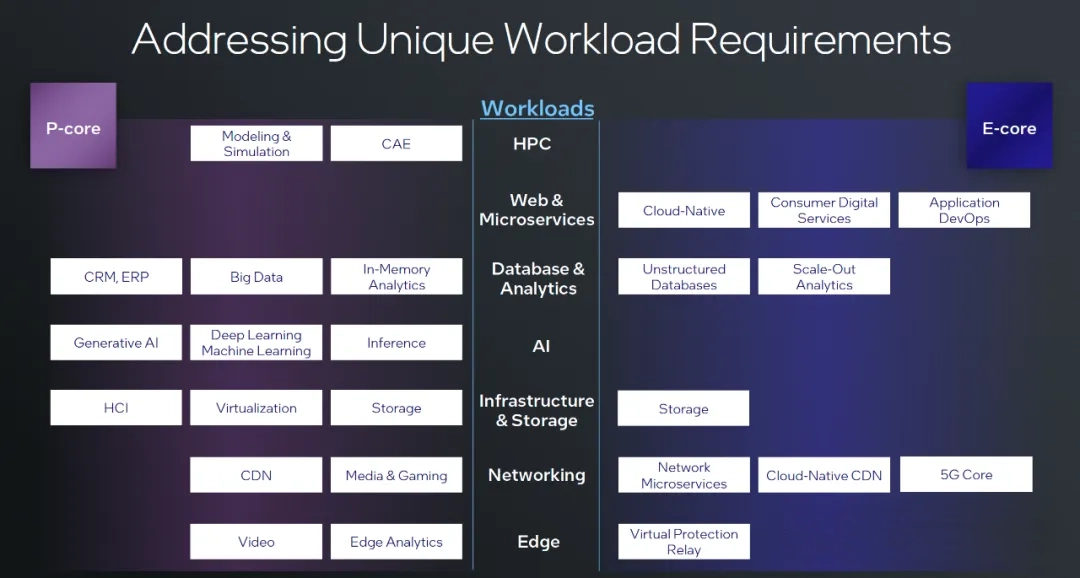

英特尔至强处理器中的性能核(P-cores)与能效核(E-cores)搭配,类似于手机处理器中的大小核架构。性能核侧重单核性能,属于纵向扩展(scale-up),能效核则注重多核心数量,属于横向扩展(scale-out)。在单核性能足够的前提下,每个能效核更为节能,同时聚合更多核心数,堪称“便宜又大碗”的解决方案。

英特尔在PC市场的酷睿处理器早已实现了P核 + E核的组合,但用于服务器的至强处理器则采用了独立的P核版和E核版。尽管E核的单核性能不及P核,但其多核优势使其非常适合微服务和云原生应用。

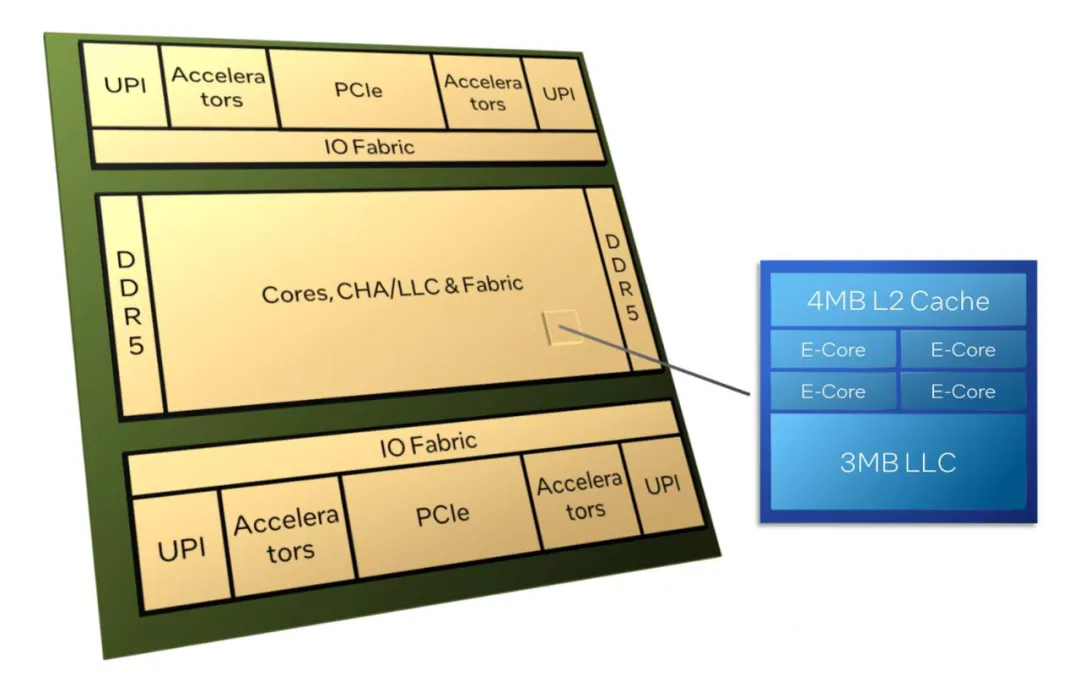

与P核相比,E核去掉了超线程功能(英特尔相当实在),每个E核仅支持一个线程。通过缩减Cache容量和向量计算单元规格来减小CPU核心面积,这是E核的显著特点:

L2 Cache容量:4个E核共享4MB,而每个P核有2MB。由于P核支持超线程,分摊到逻辑处理器上,每“核”1MB,但在物理处理器层面,P核容量是E核的两倍。L3 Cache容量进一步凸显了P核的优势。

AI和向量操作方面:P核不仅配备两个AVX-512运算单元,从Sapphire Rapids起新增的AMX矩阵引擎也加入了FP16支持;而E核则“回退”到256位的AVX2,虽然加入了INT8和BF16/FP16的VNNI(向量神经网络指令)支持,但总体算力仍远不及P核。

因此,高性能计算(HPC)和人工智能(AI)应用成为E核的两大盲区,而P核则依旧是这类应用的不二之选。

模块化架构:至强6的灵活演进

尽管至强6在核心微架构上存在显著差异,但其模块化SoC架构允许P核与E核共享同一框架,复用不同的模块(die),按需组合。这种设计提供了高度灵活性,使得不同核能够各自优化、分别演进。

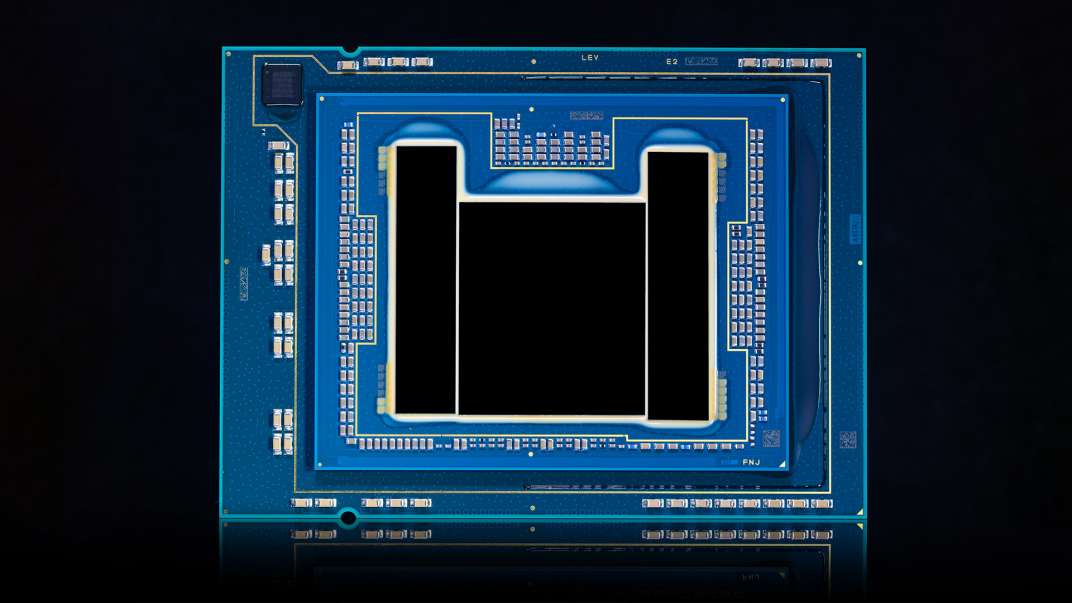

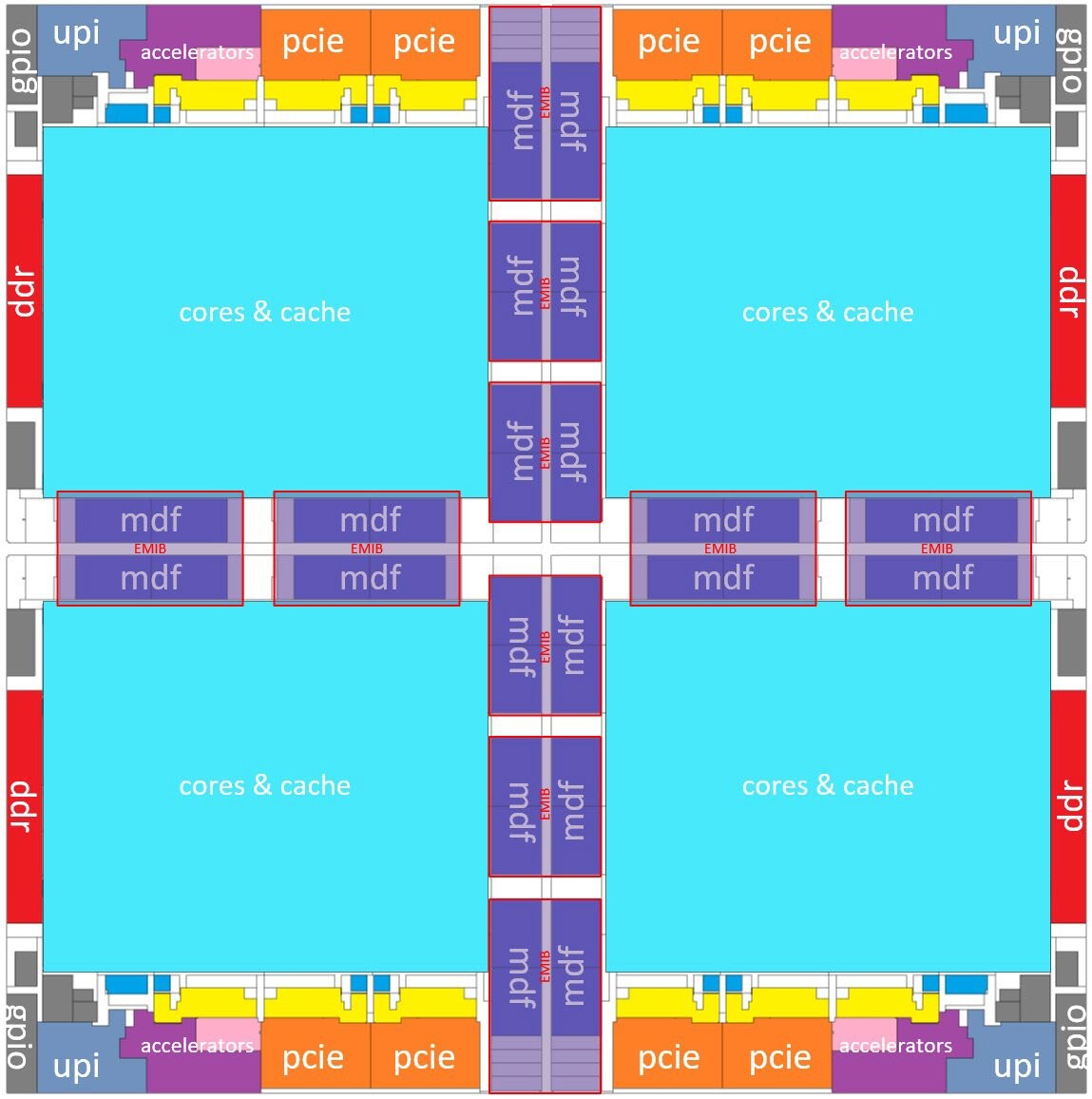

英特尔至强可扩展处理器采用的网格(Mesh)结构,在应用Chiplet技术时,网格结构不太易于拆分。网格结构的特点是将内存和I/O控制器等布置在外围,CPU核心部分则组成矩阵,初期可以将它们剥离形成单独的die,但随着矩阵规模增大,必须切分成多块(tile),即不同的die。

第四代英特尔至强可扩展处理器的四等分die布局

前两代英特尔至强可扩展处理器在网格结构中间“切开”、对等均分,从第四代的四块演进到第五代的两块,未能实现CPU核心部分(包括LLC)与内存、I/O部分的分离。

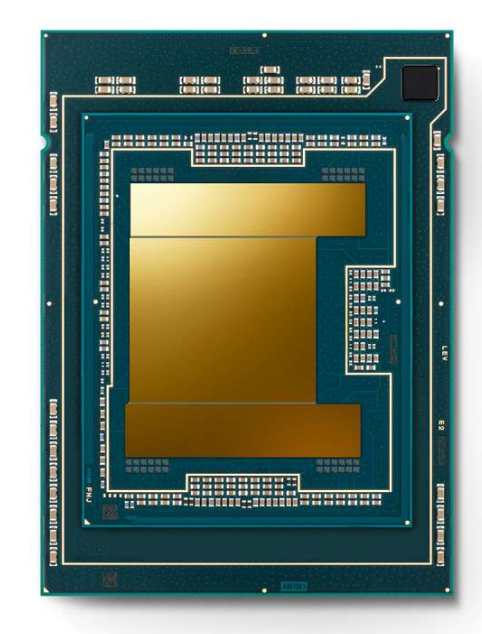

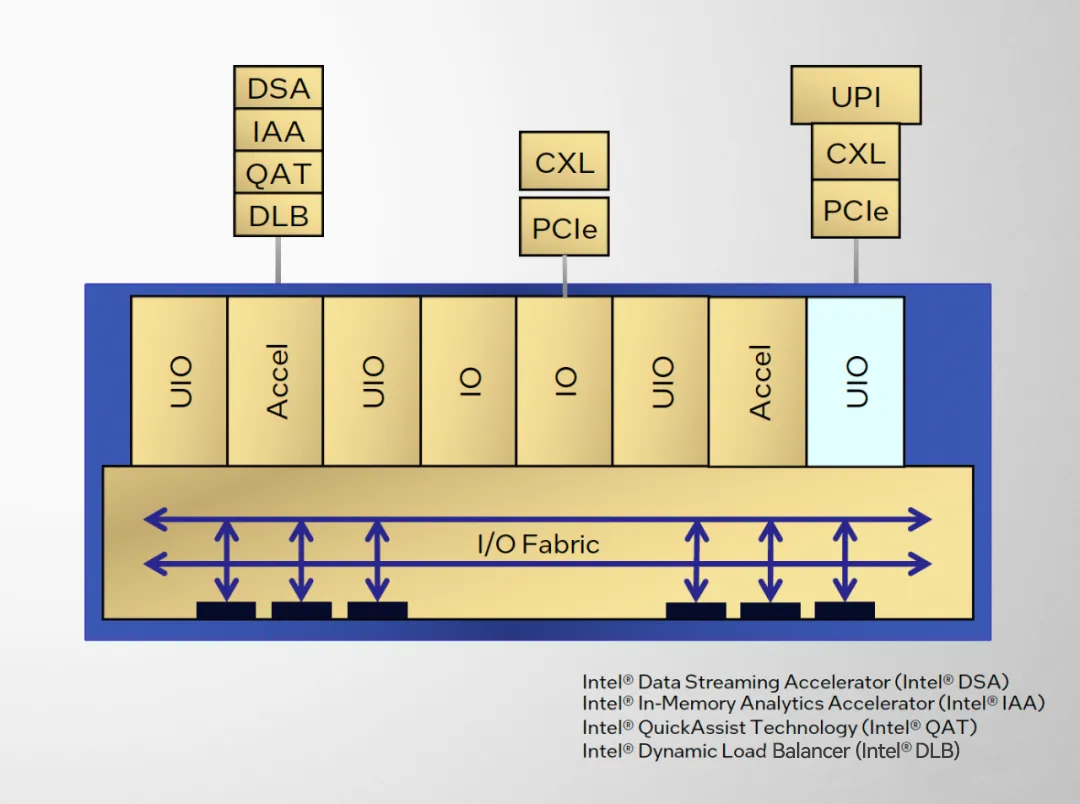

至强6改进了“刀法”,将UPI、PCIe控制器、DSA/IAA/QAT/DLB等加速器及I/O Fabric剥离为模块化的I/O die,CPU核心部分组成的矩阵与(就近的)内存控制器组成模块化的计算die。2个I/O die与1~3个计算die通过英特尔的EMIB(嵌入式多芯片互连桥接)连为一体,封装成一颗完整的处理器。

这种模块化架构不仅提高了设计的灵活性,还能根据需求灵活组合不同模块,优化整体性能表现。英特尔的这一创新设计,预示着未来处理器架构的更多可能性,为数据中心和企业应用带来了更高效、更灵活的计算解决方案。

“组核”之道:至强6的灵活设计与优化

英特尔至强6采用模块化架构,将I/O和计算分属不同的die,设计和制程可以分别优化,从而提升灵活性和性能表现。

至强 6 的 I/O die,继承了前两代留下的DSA/IAA/QAT/DLB四大加速器

I/O部分的性能从先进制程中的获益不明显,因此I/O die采用成熟的Intel 7制程,而计算die则采用先进的Intel 3制程。内存控制器与CPU核心部分一起设计,带来了至少两个好处:

时延优化:CPU核心与内存控制器的距离较近,确保时延较低。

内存规格优化:根据CPU核心的不同配置对应不同内存规格。至强6的E版支持DDR5-6400,而P版则支持速率高达8000/8800 MT/s的MCRDIMM,带宽提升25%以上。

具体到至强6700和6900(包括E版和P版),划分的主要依据是计算die的数量和两个I/O die的规格:

至强6700E:

1个E核计算die(compute tile die),最多144个E核。

至强6700P有三种构型:

LCC(Low Core Count,低核心数):1个较小的P核计算die,最多16个P核。

HCC(High Core Count,高核心数):1个计算die,最多48个P核。

XCC(eXtreme Core Count,极多核):2个计算die,最多86个P核。

至强6900E:

2个E核计算die,最多288个E核,称为ZCC。

至强6900P:

3个P核计算die,最多128个P核,称为UCC。

这种灵活的模块化设计,不仅使至强6在性能和功耗方面达到了新的高度,还能根据不同应用场景进行定制优化,为用户提供了更多的选择。英特尔在处理器设计上的创新,展现了其在计算领域的领先地位和持续创新的能力。

2个和3个,看起来E核die更方的样子

内存与能效:至强6的高效拓展

随着计算die数量的增加,处理器整体的DDR内存通道数量和最高TDP(热设计功耗)也随之增长。至强6700系列支持8个内存通道和350W的TDP,而至强6900系列则达到了12个内存通道和500W的TDP。

从单个计算die上的核心数来看,E核版的核心数量是P核版的3倍,因此核心密度显著提升。当然,P核通过超线程技术提升了逻辑处理器数量,缩小了与E核的差距。

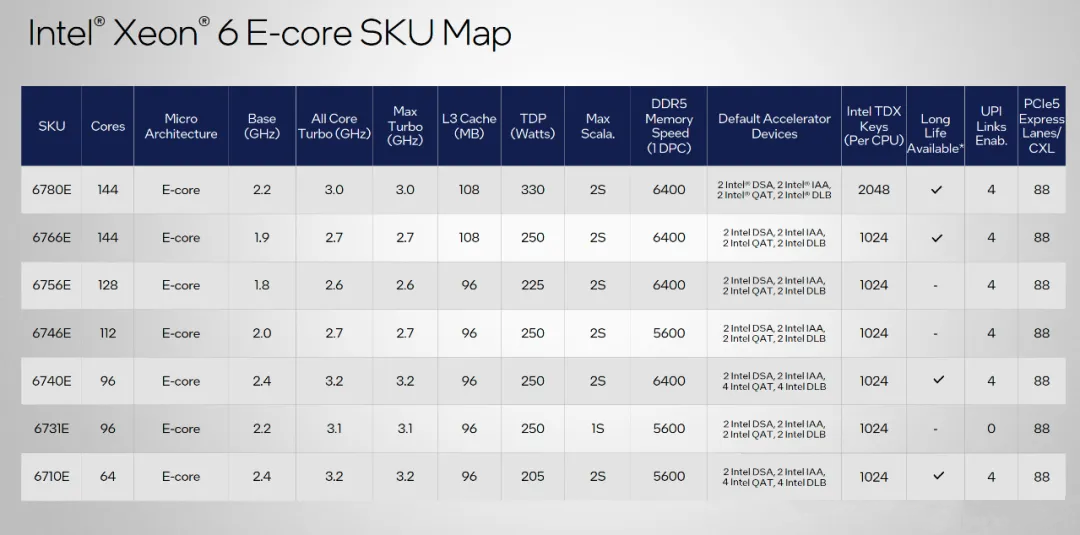

至强6700E系列成员表

由于E核计算die上的核心数较多,其单体功耗也较高。例如:

1个E核计算die的至强6780E,TDP为330W。

2个P核计算die的至强6700P,TDP为350W。

在更高端的型号中:2个E核计算die的至强6900E和3个P核计算die的至强6900P,TDP均为500W。

当然,CPU的功耗受频率等因素的影响较大,不能仅看一个指标。官方数据显示,双路配置下,与64核的第五代英特尔至强可扩展处理器旗舰8592+(TDP 350W)相比,144核的至强6780E在服务器利用率40%~60%的情况下,功耗线性增长,可以降低280W功耗,并获得18%的性能提升。

至强6700系列支持多达88个PCIe 5.0/CXL 2.0(单路可达136个)和4个UPI 2.0,P核版支持四路和八路配置。至强6900系列则增加到96个PCIe 5.0/CXL 2.0和6个UPI 2.0,但仅支持单双路配置。考虑到双路配置已经提供了200多个核心和24个内存通道,四路和八路配置的需求显得不再那么迫切。

至强6通过模块化架构实现了内存和功耗的有效管理,在保持高性能的同时,提升了能效和扩展性,为数据中心和企业应用提供了更具竞争力的解决方案。

CXL 2.0:扩展内存的新模式

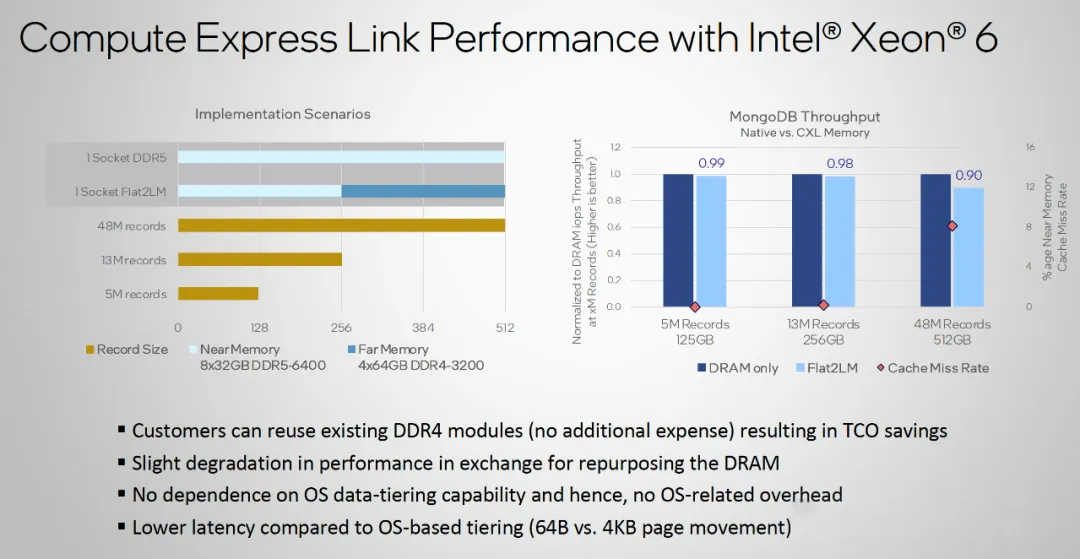

在至强6处理器中,英特尔首次引入了CXL 2.0技术,通过三种模式扩展内存:

CXL NUMA节点模式: 这种模式允许将系统原生的DRAM内存和通过CXL扩展的内存作为两个独立的NUMA节点。在系统软件或应用层进行内存内容的分层管理,优化配置,并屏蔽上层业务。这是CXL一直采用的管理模式之一。

异构交织模式(Hetero Interleaved): 这一模式针对无法对自身软件进行修改优化的客户。它将系统原生的DRAM内存和CXL内存在地址上进行混合,每个CXL内存交织的通路和DRAM交织的通路在带宽上是平衡的。虽然CXL延迟略有区别,但整体对系统的吞吐影响不大。该模式仅在6900P/6700P系列支持,提供更大的内存带宽,而应用程序不会直接感知或管理CXL内存。

扁平内存模式(Flat Memory): 这一模式通过硬件辅助将CXL和原生DRAM内存进行分层,对软件完全透明。在1:1的近/远内存比率下,会尽量将CXL常用的数据放在DRAM中,获得接近完全DRAM的性能表现。

英特尔通过MongoDB数据库业务的性能评估表明,将相对低成本的DDR4内存模组通过CXL作为远程内存,搭配本地的DDR5内存使用,性能损失不超过10%,能够有效地扩充内存容量。

这种灵活的内存扩展方案,不仅提升了内存容量,还能在性能和成本之间找到平衡点,为数据中心和企业应用提供了更多选择。英特尔的CXL 2.0技术在至强6处理器中的应用,预示着未来内存管理和扩展的新方向。

探索更多,携手共赢

如有任何问题、反馈或合作意向,请直接点击下方按钮。我们期待与您建立联系,共创美好未来。

相关资讯